Top of lower usable dram что это

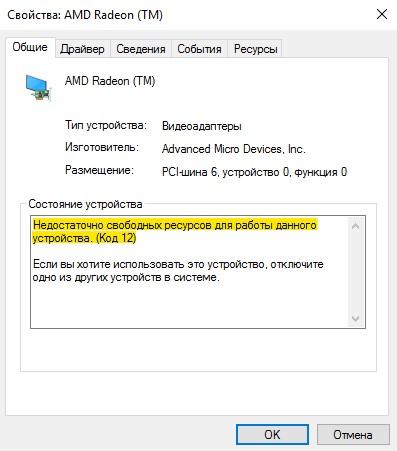

Недостаточно свободных ресурсов для работы данного устройства (Код 12)

Ошибка «Недостаточно свободных ресурсов для работы данного устройства» с кодом 12 появляется в свойствах устройства диспетчера устройств Windows 10. Она может отображаться на таких устройствах как видеокарта от Nvidia или AMD, сетевых адаптеров WiFi и Ethernet, клавиатура и мышь, или звуковых. Код 12 обозначает, что ошибка является аппаратной и возникает, когда двум устройствам назначен один и тот же порт ввода-вывода. Также, она встречается у пользователей, которые майнят криптовалюту используя два графических процессора GPU. Разберем, что делать и как исправить ошибку, когда недостаточно свободных ресурсов для работы данного устройства с кодом 12 в Windows 10.

1. Параметр TOLUD

Если вы майните криптовалюту, то система просто не заточена по умолчанию к таким специфическим настройкам. Если код 12 появляется в видеокарте Nvidia или AMD при майнинге на 2 GPU, то нужно изменить Top Of Lower Usable DRAM, который определяет верхнюю границы памяти ОЗУ, расположенной в пределах нижних четырех гигабайт адресного пространства. Войдите в BIOS и:

Воспользуйтесь Google или Яндекс картинками, чтобы найти параметры по своей модели мат. платы.

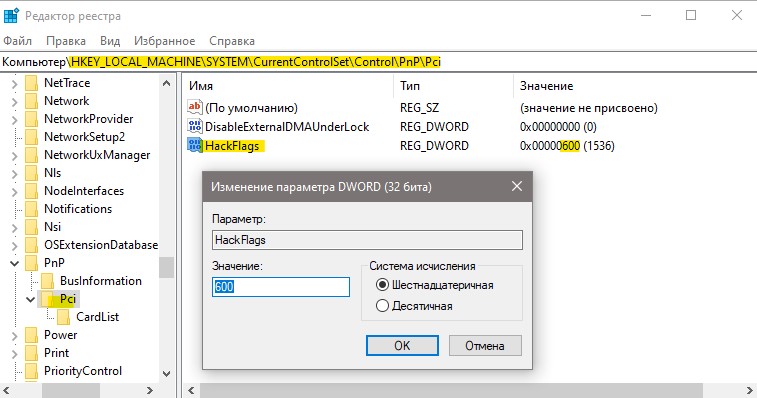

2. Реестр HackFlags

Если проблема выше способом не решилась и код 12 появляется при майнинге нескольких видеокарт, то попробуем задать значение в реестре. В первую очередь, создайте точку восстановления системы.

Нажмите Win+R и введите regedit, чтобы открыть редактор реестра. В реестре перейдите по пути:

3. Удалите драйверы PCI

Драйверы PCI связаны с материнской платой и их удаление с автоматической переустановкой может исправить проблему. Для этого:

Если не будет работать мышь или клавиатура, перегрузить Windows 10 можно одним нажатием физической кнопкой на корпусе ПК.

Win 10 32 бит, не видит весь объём озу

Система не видит весь объем ОЗУ

Установлено 4 планки ОЗУ: две планки по 2гб и две планки по 4гб, но система видит всего 8 гб.

Система в windows Домашняя. Написано. Установленная память 8ГБ. Доступно 7.87 ГБ, это потому что.

Не определяет весь объем ОЗУ

Всем здравствуйте. Конфигурация сервера: Мать Tempest i5400XT S5396 два проца Xeon E5335 RAM.

Вообщем ситуация такая что на ноуте установлено 8гб ОЗУ а отображает только 6,94(в.

Diminion, сейчас проверю планку.

Verevkin, на данной операционной системе будет установлена 1с «Розница», она то работает нормально, но вот торговое оборудование прицепленное к 1с работает некорректно на 64 битной windows, уже проверено, даже фирма производящая сопровождение 1с подтверждает, что драйвера нормальные только для 32-ух битной системы.

Добавлено через 2 минуты

на сайте производителя есть обновления биос, может обновить?

плата h110m dgs v3.0, биос версии 7.50, на сайте есть 7.70.

Есть смысл попробовать?

Добавлено через 42 секунды

изменил размер аппертуры в биос, и стало доступно 2,19 гигабайт из четырёх.

Но как понимаете это совсем ненормально)

Проникаем в Extended SMRAM или еще раз о потусторонней памяти №2

Содержание статьи

Описание работы программы

Как и в ранее опубликованных статьях данного цикла, в целях монопольного и

беспрепятственного взаимодействия программы с оборудованием при работе с

предлагаемым примером, автор применил «древнюю» технологию отладки под DOS.

Аргументация такого шага и рекомендации по организации рабочего места приведены

в ранее опубликованной статье «64-битный режим под DOS: исследовательская работа

№ 1″. Данный пример демонстрирует работу с регистрами чипсета, управляющими

доступом к памяти SMRAM. Вопросы работы с ресурсами оборудования из среды

Windows выходят за рамки данной статьи.

Программа детектирует наличие блока Extended SMRAM, и если этот блок

присутствует, визуализирует его адрес, затем сохраняет содержимое в файле

ESMRAM.BIN. Если файл с таким именем уже существует, он будет переписан. Так как

регистры управления SMRAM по-разному реализованы в каждой платформе, для

обеспечения универсальности необходимо детектировать чипсет и использовать

различные процедуры поддержки для различных платформ. В текущей версии программы

эта задача решена для частного случая – поддерживается только чипсет Intel P965.

Эксперименты проводились на материнской плате Gigabyte GA-965P-S3. Используя

предлагаемый пример как образец, заинтересованный читатель может расширить

номенклатуру поддерживаемых платформ, обратившись, например, к документам 5,

[12].

Возможность программного доступа к Extended SMRAM также зависит от того, как

BIOS инициализировал чипсет при старте платформы. Существует много платформ, где

BIOS использует только Compatible SMRAM в диапазоне адресов A0000h-BFFFFh и не

использует Extended SMRAM. На некоторых платах BIOS устанавливает бит блокировки

SMRAM, после чего регистры управления становятся недоступны для записи. Снятие

блокировки происходит только при аппаратном сбросе. Если одна из указанных

ситуаций имеет место, программа выдает соответствующее сообщение об ошибке.

Особенности чтения регистров чипсета, анализа их содержимого и детектирования

статуса SMRAM детально описаны ниже, при описании работы программы.

Прилагаемый каталог WORK содержит следующие файлы:

ASM_TD.BAT – обеспечивает ассемблирование, линковку и запуск программы под

отладчиком. При запуске TASM и TLINK используются опции, обеспечивающие

добавление отладочной информации в EXE файл и отладку с просмотром исходного

текста программы.

ASM_EXE.BAT – обеспечивает ассемблирование и линковку. Генерируется EXE файл.

R_ESMRAM.ASM – основной модуль программы. Проверяет условия запуска программы,

детектирует чипсет и анализирует его текущее состояние. Если процессор находится

в реальном режиме, чипсет распознан, память Extended SMRAM используется и не

блокирована, программа выполняет сохранение блока Extended SMRAM в файле

ESMRAM.BIN.

DOSMSG.INC – процедура вывода строки на экран с использованием функций DOS.

NUMPRINT.INC – библиотека для визуализации шестнадцатеричных и десятичных чисел.

Диапазон адресов Extended SMRAM визуализируется в шестнадцатеричном виде, размер

диапазона – в десятичном виде.

PCIBIOS.INC – библиотека для чтения и записи регистров конфигурационного

пространства PCI. Используется при работе с регистрами чипсета.

A20.INC – Библиотека для управления и контроля состояния адресной линии A20 с

использованием выходного порта контроллера клавиатуры.

BIGREAL.INC – Библиотека поддержки режима Big Real Mode, для использования

32-битных адресов в диапазоне 0-4 Гб. Этот режим, как и управление адресной

линией A20, необходимы в данной программе для доступа к Extended SMRAM.

DATASEGS.INC – сегменты данных, адресуемые в реальном режиме с использованием

16-битных адресов: сегмент для хранения переменных и текстовых строк (DATA_16),

буфер для чтения SMRAM (BUFFER_16), а также сегмент стека (STACK_16). Базовый

адрес сегмента BUFFER_16 выровнен на границу параграфа (кратен 16), это дает

возможность использовать нулевой стартовый адрес указателя, и обеспечивает

некоторый прирост производительности при операциях пересылки блоков данных.

При возникновении противоречия между наглядностью и оптимальностью кода, автор

выбирал наглядность. Код может быть модифицирован и оптимизирован в соответствии

со спецификой конкретной задачи.

1) Установка адреса стека, загрузка регистров SS и SP.

2) Проверка режима работы процессора. Программа требует Real Mode, так как

взаимодействует с аппаратными ресурсами платформы. Если процессор в Protected

Mode, завершаем работу с сообщением об ошибке.

3) Детектирование чипсета. Вначале проверяем наличие PCIBIOS, затем считываем

регистры конфигурационного пространства Vendor ID и Device ID микросхемы

«северного моста» чипсета. Если Vendor Device чипсет Intel

P965 детектирован, продолжаем выполнение. Иначе завершаем работу с сообщением об

ошибке. Подробности в 14.

4) Детектирование статуса Extended SMRAM. Считываем регистры конфигурационного

пространства SMRAM Control Register и Extended SMRAM Control Register.

Проверяем, что бит Global SMRAM Enable (бит 3 регистра SMRAM Control Register)

установлен в «1». Это означает, что SMRAM используется. Также проверяем, что бит

TSEG Enable (бит 0 регистра Extended SMRAM Control Register) установлен в «1».

Это означает, что Extended SMRAM используется. Затем проверяем, что SMRAM не

блокирована, то есть бит SMM Space Locked (бит 4 регистра SMRAM Control

Register) установлен в «0». Если память Extended SMRAM не используется или

блокирована, завершаем работу с сообщением об ошибке. Подробности в [1].

5) Установка адреса сегмента данных, загрузка регистра DS. Сегмент DATA_16

содержит переменные, константы и текстовые строки.

6) Определение размера Extended SMRAM. Для этого анализируем биты TSEG Size

(биты 2,1 регистра Extended SMRAM Control Register). Рассматриваемый чипсет

Intel P965 поддерживает значения размера 1, 2 и 8 MB.

7) Определение базового адреса Extended SMRAM. Считываем регистр TSEG Memory

Base, содержимое которого численно равно адресу.

8) Дополнительная верификация размера Extended SMRAM. Считываем регистр TOLUD

(Top of Low Usable DRAM), по содержимому которого определяем верхнюю физическую

границу диапазона доступа к оперативной памяти. Разность между адресом верхней

физической границы оперативной памяти и базовым адресом Extended SMRAM является

размером Extended SMRAM. Сравниваем это значение с полученным в пункте 6 и

сохраняем для последующего использования меньшее из двух значений размера.

9) Подготовка и вывод строки, описывающей начальный адрес, конечный адрес и

размер блока Extended SMRAM.

10) Вывод строки с запросом к пользователю: ESC-выход без сохранения файла,

ENTER-сохранить Extended SMRAM в файле ESMRAM.BIN. Ожидание и обработка ввода с

клавиатуры.

11) Создание файла ESMRAM.BIN.

12) Установка позиции курсора для отображения адресов при сохранении файла

ESMRAM.BIN.

Пункты 13-20 образуют цикл, используемый для сохранения Extended SMRAM в файле.

За одну итерацию сохраняется 32 килобайта. Полный размер Extended SMRAM в

зависимости от конфигурации составляет 1-8 мегабайт.

13) Отображение адресов текущего сохраняемого блока.

14) Подготовка к 32-битной адресации. Разрешаем адресную линию A20 и включаем

режим Big Real Mode. Это необходимо для доступа к памяти Extended SMRAM, так как

она расположена выше 1MB. Исходное состояние линии A20 сохраняем для

последующего восстановления.

15) Открытие SMRAM. Устанавливаем бит SMM Space Open в «1» (бит 6 регистра SMRAM

Control Register). Это обеспечивает такое состояние «северного моста» чипсета,

при котором все обращения в диапазоны адресов Compatible SMRAM и TSEG будут

направляться на шину оперативной памяти. Исходное значение указанного регистра

сохраняем для последующего восстановления. Предварительно запрещаем прерывания,

так как в указанном состоянии чипсета, запуск процедур обработки прерываний

может привести к сбою.

16) Копирование 32-килобайтного блока из региона TSEG в транзитный буфер.

Выполняется инструкция REP MOVS с 32-битной адресацией. Предварительно

выполняется инструкция WBINVD, обеспечивающая очистку кэш-памяти. Отметим, что в

кэш-памяти могла остаться информация, прочитанная из региона TSEG до открытия

SMRAM. Если не выполнить очистку, процессор будет использовать «устаревшую»

копию TSEG, находящуюся в кэш-памяти вместо физического чтения TSEG.

17) Восстановление исходного значения регистра SMRAM Control Register. После

этого прерывания разрешаются.

18) Выключение режима Big Real Mode и восстановление исходного состояния

адресной линии A20.

19) Содержимое транзитного буфера, в который при выполнении пункта 16 была

скопирована очередная 32-килобайтная порция данных из региона TSEG, дописываем в

файл ESMRAM.BIN, созданный при выполнении пункта 11.

20) Организация цикла, увеличиваем адрес на 32 килобайта и переходим к пункту

13, пока не будет обработан весь регион TSEG.

21) Закрытие файла ESMRAM.BIN.

22) Выдача сообщения об успешном завершении программы и выход в DOS.

23) Точка выхода для прерывания работы программы по нажатию ESC.

Пункты 24-35 обеспечивают аварийное завершение программы. Сюда передается

управление при различных ошибках. Выполняется выдача сообщения об ошибке и выход

в DOS. Если ошибка возникла в момент, когда состояние системных ресурсов

(например, адресной линии A20) было изменено, перед выходом в DOS выполняется

также восстановление исходного состояния.

После выполнения программы, если память Extended SMRAM используется и не

заблокирована, на диске появится файл ESMRAM.BIN, размером от 1 до 8 Мегабайт.

Размер и содержимое файла зависят от того, как BIOS на данной платформе

использует ESMRAM.

Если SMM Locked

Как было показано выше, если установлен бит SMM Space Locked (бит 4 регистра

SMRAM Control Register), то установить состояние SMM Space Open и прочитать

содержимое Extended SMRAM невозможно. Программно обнулить бит SMM Space Locked

также невозможно, он обнуляется только при аппаратном сбросе. Можно ли обойти

эту защиту?

Один из вариантов – перепрограммирование регистров DRB (DRAM Row Boundary), с

помощью которых каждому физическому банку памяти присваивается свой диапазон

адресов. Подробности в [1]. Таким образом, можно добиться того, что регион

оперативной памяти, содержащий SMRAM «появится» в таком регионе адресного

пространства, который не защищен логикой поддержки SMM. Но сделать это

достаточно сложно из-за многочисленных побочных эффектов, так как все, что

находится в оперативной памяти, включая ОС, приложения и саму программу,

выполняющую эту операцию, будет искажено на время «измененного состояния чипсета», а возможно и после восстановления исходного состояния. Конечно, наша

программа может, например, переписать себя в видео память или заблокироваться в

кэш-памяти и таким образом пережить сбой оперативной памяти. Автор планирует

описать такую процедуру в последующих публикациях…

Источники информации

Электронные документы, доступные на сайте

developer.intel.com.

1) Intel P965 Express Chipset Family Datasheet – For the Intel 82P965 Memory

Controller Hub (MCH). Document Number: 313053-001.

2) Intel I/O Controller Hub 8 (ICH8) Family Datasheet – For the Intel 82801HB

ICH8 and 82801HR ICH8R I/O Controller Hubs. Document Number: 313056-001.

3) Intel Core 2 Extreme Processor X6800 and Intel Core2 Duo Desktop Processor

E6000 and E4000 Sequences Datasheet. Document Number: 313278-004.

4) Intel Core i7 Processor Extreme Edition and Intel Core i7 Processor Datasheet,

Volume 1. Document Number: 320834-001.

5) Intel Core i7 Processor Extreme Edition and Intel Core i7 Processor Datasheet,

Volume 2. Document Number: 320835-002.

Электронные документы, доступные на сайте

developer.amd.com.

6) BIOS and Kernel Developer’s Guide for AMD NPT Family 0Fh Processors.

Publication No. 32559.

7) BIOS and Kernel Developer’s Guide (BKDG) for AMD Family 10h Processors.

Publication No. 31116.

8) AMD Functional Data Sheet, 754 Pin Package. Publication # 31410.

9) AMD Functional Data Sheet, 939 Pin Package. Publication # 31411.

10) AMD Functional Data Sheet, 940 Pin Package. Publication # 31412.

Электронные документы, доступные на сайте

www.hypertransport.org.

11) HyperTransport I/O Link Specification. Revision 3.00. Document #

HTC20051222-0046-0008.

Электронные документы, доступные на сайте

datasheetarchive.com.

(Информация на данном сайте более полная, чем на «родных» сайтах

производителей указанных микросхем.)

12) VIA P4X400 Chipset. VT8754 Single-Chip North Bridge. Для поиска документа

набирать строку «P4X400», «P4X533» или «VT8754».

Электронные документы, доступные на сайте

pcisig.com.

Документы [14], [15] на сайте pcisig.com доступны только для членов PCI

Special Interest Group. Воспользовавшись поисковыми системами, можно найти

данные документы для свободной загрузки.

13) PCI BIOS Specification. Revision 2.1.

14) PCI Local Bus Specification. Revision 3.0.

15) PCI-to-PCI Bridge Architecture Specification. Revision 1.1.

Книги

16) В.Л. Григорьев. Микропроцессор i486. Архитектура и программирование.

Москва ТОО «ГРАНАЛ» 1993.

17) М. Гук. Аппаратные средства IBM PC. Энциклопедия. Санкт-Петербург,

издательство «Питер» 2006.

Проникаем в Extended SMRAM или еще раз о потусторонней памяти №1

Содержание статьи

Напомним, что первые реализации SMM, появившиеся еще в процессорах класса 486

использовали 128 Кб памяти SMRAM, которая располагалась в диапазоне адресов

A0000h-BFFFFh. В этом же диапазоне адресуется видео память, поэтому в обычном

режиме (не SMM) память SMRAM недоступна в адресном пространстве, что также

обеспечивает ее защищенность от несанкционированной модификации. При обработке

прерывания System Management Interrupt (SMI), процессор переходит в режим SMM и

на указанный диапазон включается SMRAM.

Главным потребителем SMRAM является BIOS. Так как функциональность и набор

обязанностей BIOS постоянно расширяются, 128 Кб SMRAM уже недостаточно для ряда

современных платформ. Двойное использование диапазона A0000h-BFFFFh для SMRAM и

видео памяти также доставляет ряд неудобств. Поэтому появились новые механизмы

адресации памяти SMRAM, обеспечивающие увеличение ее размера и дополнительную

гибкость при адресации. Рассмотрению этих механизмов посвящена данная статья.

Материал проиллюстрирован исходными текстами программы, сохраняющей образ

Extended SMRAM в двоичном файле.

Чтобы не повторяться, автор концентрирует внимание на новых типах памяти

SMRAM – регионах TSEG (Top Segment) и HSEG (High Segment). Читателю, не

знакомому с основными принципами организации SMM и SMRAM, рекомендуется сначала

обратиться к ранее опубликованной статье.

Регион TSEG или Extended SMRAM

Подобно региону Compatible SMRAM, рассмотренному в ранее опубликованной

статье, регион TSEG реализован как специальная область оперативной памяти,

возможность доступа к которой зависит от текущего режима работы процессора. В

обычном режиме (не SMM), доступ блокирован, по всем адресам региона считывается

FFh, запись игнорируется. В режиме SMM доступ осуществляется как к обычной

оперативной памяти. При установке специального состояния SMRAM Open, доступ к

этому региону открыт независимо от режима работы процессора. Это облегчает

задачу инициализации SMRAM для BIOS, а также используется в прилагаемой к статье

программе для чтения содержимого SMRAM.

В отличие от Compatible SMRAM, регион TSEG расположен в «верхней» памяти, его

базовый адрес и размер программируются и при доступе к нему разрешено

кэширование, что способствует повышению производительности при выполнении

процедур в режиме SMM.

Регион HSEG

Регион HSEG расположен выше верхней физической границы диапазона оперативной

памяти и используется как альтернативное окно для доступа к Compatible SMRAM.

Например, для большинства чипсетов Intel он находится по фиксированным адресам

FEDA0000h-FEDBFFFFh. При обращении процессора в данный диапазон, чипсет

преобразует адрес и на оперативную память подается адрес 000A0000h-000BFFFFh,

обеспечивающий доступ к Compatible SMRAM.

Преимущества по сравнению с обычным доступом к Compatible SMRAM – отсутствие

конфликта адресов с видео памятью и использование кэширования.

Архитектура доступа к SMRAM на примере чипсета Intel P965

Рассмотрим регистры, управляющие доступом к SMRAM, входящие в состав

«северного моста» чипсета Intel P965 (это микросхема Intel 82P965 Memory

Controller Hub). Детальное описание микросхем данного чипсета приведено в [1,2].

Механизм доступа в конфигурационное пространство описан в 13.

Регистр SMRAM Control Register имеет адрес в конфигурационном пространстве

Bus=0, Device=0, Function=0, Register=9Dh. Разрядность – 8 бит. Назначение битов

следующее:

Бит 7 (Reserved) зарезервирован, не используется.

Бит 6 (SMM Space Open) управляет доступом к памяти SMRAM в режиме не SMM. При

установке данного бита в «1», доступ к SMRAM открыт, независимо от режима работы

процессора. При установке в «0» обращение к SMRAM возможно только в режиме SMM.

Бит 5 (SMM Space Closed) управляет выполнением циклов чтения и записи данных

в режиме SMM. При установке «1» циклы чтения и записи данных направляются на

шину ввода-вывода, а циклы чтения команд – на шину памяти. Это позволяет

программе, выполняемой в режиме SMM из диапазона адресов A0000h-BFFFFh

обращаться к видео памяти несмотря на то, что Compatible SMRAM и видео память

используют один и тот же диапазон адресов. При установке «0» все виды обращений

к SMRAM направляются на оперативную память.

Бит 4 (SMM Space Locked) позволяет защитить регистры, управляющие доступом к

SMRAM от несанкционированной модификации. При установке «1» в этом бите,

указанные регистры становятся недоступными для записи, а бит SMM Space Open

принудительно обнуляется. В таком состоянии чипсет будет блокирован до

аппаратного сброса, так как программно обнулить бит SMM Space Locked невозможно.

Данный механизм обеспечивает достаточно эффективную защиту, но на большинстве

платформ, исследованных автором, BIOS его не использует.

Бит 3 (Global SMRAM Enable) управляет доступом ко всем видам памяти SMRAM (Compatible,

TSEG, HSEG). Установка «1» в этом бите разрешает использование SMRAM в режиме

SMM. При «0» доступ к SMRAM запрещен, независимо от режима работы процессора.

Биты 2-0 (Compatible SMM Base Segment) зарезервированы для управления

расположением памяти Compatible SMRAM. В рассматриваемом чипсете ее расположение

фиксировано – A0000h-BFFFFh, а данное битовое поле зафиксировано в состоянии

«010».

Регистр Extended SMRAM Control Register имеет адрес в конфигурационном

пространстве Bus=0, Device=0, Function=0, Register=9Eh. Разрядность – 8 бит.

Назначение битов следующее:

Бит 6 (Invalid SMRAM Access) статусный бит, который аппаратно устанавливается

в «1» если имели место «незаконные» обращения процессора к регионам TSEG и HSEG,

то есть не в режиме SMM и не в состоянии SMM Space Open. Для обнуления этого

бита, программа должна записать «1» в него.

Биты 2-1 (TSEG Size) управляет размером диапазона TSEG, биты интерпретируются

следующим образом: 00 = 1 Мб, 01 = 2 Мб, 10 = 8 Мб, 11 = не используется.

Бит 0 (TSEG Enable) управляет доступом к памяти Extended SMRAM (TSEG).

Установка «1» в этом бите разрешает использование Extended SMRAM в режиме SMM.

При «0» доступ к Extended SMRAM запрещен, независимо от режима работы

процессора. Для использования Extended SMRAM, бит Global SMRAM Enable в регистре

SMRAM Control Register также должен быть установлен в «1».

Регистр TSEG Memory Base имеет адрес в конфигурационном пространстве Bus=0,

Device=0, Function=0, Register=ACh. Разрядность – 32 бита. Содержимое этого

регистра определяет базовый адрес региона TSEG. Биты 31-20 доступны для

перезаписи, биты 19-0 зафиксированы в «0», поэтому адрес всегда кратен 1 MB. Для

рассматриваемого чипсета регион TSEG всегда должен располагаться в последнем

блоке оперативной памяти, примыкающем к ее верхней физической границе, которая

задается с помощью регистра TOLUD.

Регистр TOLUD (Top of Low Usable DRAM) имеет адрес в конфигурационном

пространстве Bus=0, Device=0, Function=0, Register=B0h. Разрядность – 16 бит.

Содержимое этого регистра определяет верхнюю физическую границу оперативной

памяти. Биты 15-4 доступны для перезаписи и соответствуют битам адреса 31-20.

Биты 3-0 зафиксированы в «0».

Примечание

Под верхней физической границей оперативной памяти здесь понимается граница,

расположенная в пределах нижних 4 Гб между регионом доступа к оперативной памяти

и регионом Memory-mapped I/O, также расположенным в пределах нижних 4 Гб. В

рассматриваемом чипсете все виды памяти SMRAM находятся в пределах нижних 4 Гб.

Оперативная память, расположенная выше 4 Гб, и регистры, управляющие ее

расположением и размером, не затрагиваются в наших рассуждениях.

Регион TSEG и проблема когерентности кэш-памяти

Напомним, что регион TSEG, используемый для доступа к Extended SMRAM,

кэшируется как обычная оперативная память с целью повышения производительности.

Это означает, что когда процессор читает информацию из этого региона, копия

прочитанной информации может оставаться в кэш-памяти и при последующих

обращениях по тем же адресам, вместо чтения оперативной памяти процессор

прочитает информацию из своей кэш-памяти, которая работает значительно быстрее.

Напомним также, что в зависимости от состояния бита SMM Space Open в (бит 6

регистра SMRAM Control Register) чипсет по-разному обрабатывает обращение к

региону TSEG. При SMM Space Open=0 доступ закрыт и по всем адресам считывается

значение FFh. При SMM Space Open=1 доступ открыт, чтение и запись оперативной

памяти выполняется обычным образом.

Теперь представим себе, что за время рабочего сеанса, программа обращалась к

региону TSEG при SMM Space Open=0 и в кэш-памяти осталась копия содержимого

этого региона, затем программа открывает SMRAM, устанавливая бит SMM Space Open=1,

и читает из региона TSEG, рассчитывая получить информацию из оперативной памяти

Extended SMRAM. Чтобы «увидеть» изменившееся после открытия SMRAM содержимое

региона TSEG, процессор должен обратиться к памяти, выполнив соответствующие

транзакции на системной шине. Но если копия информации, которую необходимо

прочитать, имеется в кэш-памяти, то вместо транзакций на системной шине чтение

будет выполнено из кэш-памяти внутри процессора. В результате будет прочитана

«устаревшая» копия региона TSEG. Для программы это будет выглядеть так, как

будто бы открытия SMRAM не произошло.

Одно из решений этой проблемы – очистить кэш-память между операциями открытия

SMRAM и чтения региона TSEG, применив инструкцию WBINVD (Write Back and

Invalidate Cache). Такое решение используется в программе, прилагаемой к статье.

При работе Bus Master устройств аппаратно выполняется операция Cache

Invalidation, суть которой в том, что адреса ячеек памяти, в которые

осуществляется запись, передаются в процессор и анализируются контроллером

кэш-памяти. При этом ячейки кэш-памяти, хранящие копии ячеек оперативной памяти,

перезаписанных Bus Master устройством, автоматически объявляются недостоверными.

При запрете и разрешении адресной линии A20 проблем с кэш-памятью не

возникает потому что операция маскирования A20 выполняется внутри процессора и

адрес, получаемый контроллером кэш-памяти, уже откорректирован в соответствии со

статусом линии A20. Сигнал маскирования Gate A20 передается от внешних схем

управления на процессор в явном виде, например, на Socket 775 (Intel) это

контакт с координатами K3, подробности в [3]. Либо для управления маскированием

используются специальные сообщения, передаваемые от чипсета к процессору по

системной шине, такой принцип используется в процессорах классов Socket 1366 (Intel),

Socket 754/939/940/AM2/AM3 (AMD), подробности в 4, 6.

В отличие от двух выше описанных ситуаций, аппаратных средств, гарантирующих

достоверность информации в кэш-памяти при работе с регионом TSEG, не

предусмотрено. Именно поэтому, кэш-память нужно очищать программно.

Источники информации

Электронные документы, доступные на сайте

developer.intel.com.

1) Intel P965 Express Chipset Family Datasheet – For the Intel 82P965 Memory

Controller Hub (MCH). Document Number: 313053-001.

2) Intel I/O Controller Hub 8 (ICH8) Family Datasheet – For the Intel 82801HB

ICH8 and 82801HR ICH8R I/O Controller Hubs. Document Number: 313056-001.

3) Intel Core 2 Extreme Processor X6800 and Intel Core2 Duo Desktop Processor

E6000 and E4000 Sequences Datasheet. Document Number: 313278-004.

4) Intel Core i7 Processor Extreme Edition and Intel Core i7 Processor Datasheet,

Volume 1. Document Number: 320834-001.

5) Intel Core i7 Processor Extreme Edition and Intel Core i7 Processor Datasheet,

Volume 2. Document Number: 320835-002.

Электронные документы, доступные на сайте

developer.amd.com.

6) BIOS and Kernel Developer’s Guide for AMD NPT Family 0Fh Processors.

Publication No. 32559.

7) BIOS and Kernel Developer’s Guide (BKDG) for AMD Family 10h Processors.

Publication No. 31116.

8) AMD Functional Data Sheet, 754 Pin Package. Publication # 31410.

9) AMD Functional Data Sheet, 939 Pin Package. Publication # 31411.

10) AMD Functional Data Sheet, 940 Pin Package. Publication # 31412.

Электронные документы, доступные на сайте

www.hypertransport.org.

11) HyperTransport I/O Link Specification. Revision 3.00. Document #

HTC20051222-0046-0008.

Электронные документы, доступные на сайте

datasheetarchive.com.

(Информация на данном сайте более полная, чем на «родных» сайтах

производителей указанных микросхем.)

12) VIA P4X400 Chipset. VT8754 Single-Chip North Bridge. Для поиска документа

набирать строку «P4X400», «P4X533» или «VT8754».

Электронные документы, доступные на сайте

pcisig.com.

Документы [14], [15] на сайте pcisig.com доступны только для членов PCI

Special Interest Group. Воспользовавшись поисковыми системами, можно найти

данные документы для свободной загрузки.

13) PCI BIOS Specification. Revision 2.1.

14) PCI Local Bus Specification. Revision 3.0.

15) PCI-to-PCI Bridge Architecture Specification. Revision 1.1.

Книги

16) В.Л. Григорьев. Микропроцессор i486. Архитектура и программирование.

Москва ТОО «ГРАНАЛ» 1993.

17) М. Гук. Аппаратные средства IBM PC. Энциклопедия. Санкт-Петербург,

издательство «Питер» 2006.