Usb controllers 1 xhci что это

XHCI EHCI UHCI OHCI что это такое и в чём разница

XHCI EHCI UHCI OHCI это интерфейсы USB-контроллера в составе платформы персонального компьютера, который обеспечивает коммуникацию с периферийными устройствами, подключенными к универсальной последовательной шине.

USB-контроллер является устройством, способным взаимодействовать с оперативной памятью в обход центрального процессора в режиме прямого доступа к памяти.

По способу интеграции контроллер для USB-шины может быть задействован в составе системной логики или в виде дискретного чипа как на самой системной плате, так и на плате расширения. По способу подключения USB-контроллер может быть выполнен для PCI-шины, либо для шины PCI Express.

UHCI OHCI для USB 1.1

В рамках спецификации USB 1.1 существуют две реализации контроллера для USB-шины: UHCI (Universal Host Controller Interface, создан Intel для USB 1.0) и OHCI (Open Host Controller Interface), которые отличаются методом доступа к регистрам. Регистры UHCI находятся в пространстве портов ввода-вывода, а регистры OHCI адресуются в пространстве памяти.

Контроллер OHCI более интеллектуален по сравнению с UHCI. Это касается его способности освободить центральный процессор от выполнения рутинных операций по передаче данных по USB-шине. Оба контроллера используют 32-битную адресацию в пределах младших 4 ГБ адресного пространства, ни один из них не поддерживает 64-битный режим адресации.

EHCI в USB 2.0

Для USB 2.0 был разработан EHCI (Enhanced Host Controller Interface), который поддерживает только работу на высокой скорости (high speed, 480 Мбит/с).

В EHCI-контроллере с помощью разделенных транзакций (Split Transaction) реализована также поддержка низкоскоростных интерфейсов USB 1.1 для работы с более медленными устройствами.

XHCI для USB 3.0

Для USB 3.0 используется универсальный интерфейс XHCI (eXtensible Host Controller Interface), который поддерживает все скорости обмена данными.[1] Windows 7 при установке с USB не поддерживает USB 3.0 и просит драйвера носителя, проблема решается отключением в BIOS поддержки USB 3.0 или xHCI или подстановкой драйверов USB-контроллера при установке.

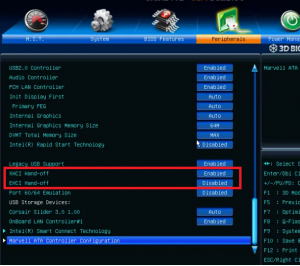

Что такое XHCI hand off в настройках BIOS?

Опция xhci hand off практически всегда встречается в современных материнских платах, на которых реализованы порты USB 3.0. Также данную опцию часто путают с EHCI Hand-Off. Обе они обычно имеют два состояния – Enabled (включено) и Disabled (выключено). Реже бывает значение AUTO.

В данной статье мы расскажем вам о назначении каждой из выше описанных опций, а также когда и какую из них нужно включать.

Для чего нужны EHCI Hand-Off и XHCI hand off?

Обе данные опции отвечают за включение и отключение функции контроля передачи управления контроллером USB от BIOS к операционной системе.

Разница между ними заключается в том, что EHCI Hand-Off (расшифровывается как Enhanced Host Controller Interface) контролирует передачу управления контроллера USB 2.0, а XHCI Hand Off (eXtensible Host Controller Interface) – контроллера USB 3.0.

Стоит обратить внимание на тот факт, что usb порты работают как в BIOS, так и в операционной системе. Так вот до того, как начнет грузится ОС работой контроллера USB управляет BIOS, а после загрузки ОС передает управление контроллером ей.

Ранее в этот самый момент передачи управления могли возникать проблемы и ошибки. Чтобы ошибки исключить и были придуманы опции EHCI Hand-Off и XHCI Hand Off. Последняя является продолжением первой, так как современные материнские платы имеют на своем борту eXtensible Host Controller Interface – usb контроллер, поддерживающий работу с USB 3.0.

Какое значение выставлять?

Что касается старого EHCI Hand-Off, то, начиная с Windows XP, ей нужно выставлять значение Disabled, так как механизм контроля и исключения ошибок при передачи управления контроллером USB 2.0 был интегрирован в операционную систему.

Правильные значениях для опций XHCI hand off и EHCI Hand-Off

Что касается опции XHCI Hand Off, то здесь все наоборот. Она должны быть всегда включена вне зависимости от версии операционной системы. По умолчанию включена практически на всех материнских платах.

Ее отключение может привести к сбоям в работе USB портов, а также устройств, подключенным к ним.

xHCI улучшает уже существующие архитектуры Open Host Controller Interface (OHCI) и Universal Host Controller Interface (UHCI), что наиболее заметно в обработке более широкого диапазона скоростей в рамках единого стандарта, в более эффективном управлении ресурсами в интересах мобильных хостов с помощью ограниченные ресурсы питания (например, планшеты и сотовые телефоны), а также упрощение поддержки смешивания низкоскоростных и высокоскоростных устройств.

СОДЕРЖАНИЕ

Архитектурные цели

XHCI является радикальным отходом от предыдущих поколений архитектур интерфейса хост-контроллера USB (то есть открытого интерфейса хост-контроллера (OHCI), универсального интерфейса хост-контроллера (UHCI) и расширенного интерфейса хост-контроллера (EHCI)) во многих отношениях. Ниже приведены ключевые цели архитектуры xHCI:

Архитектурные детали

Поддержка всех скоростей

Контроллеры OHCI и UHCI поддерживают только устройства со скоростью USB 1 (1,5 Мбит / с и 12 Мбит / с), а EHCI поддерживает только устройства USB 2 (480 Мбит / с).

Архитектура xHCI была разработана для поддержки всех скоростей USB, включая SuperSpeed (5 Гбит / с) и будущие скорости, в рамках одного стека драйверов.

Энергоэффективность

Поддержка виртуализации

Упрощенная архитектура драйвера

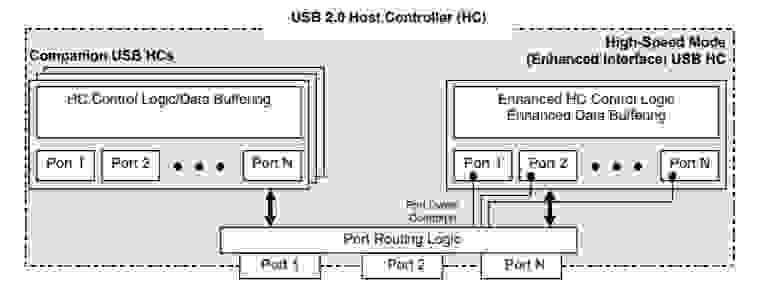

EHCI использует контроллеры OHCI или UHCI в качестве «сопутствующих контроллеров», где устройства USB 2 управляются через стек EHCI, а логика порта EHCI позволяет маршрутизировать низко- или полноскоростное USB-устройство к порту «сопутствующий» контроллер UHCI или OHCI, в котором низко- или полноскоростные USB-устройства управляются через соответствующий стек UHCI или OHCI. Например, плата хост-контроллера USB 2 PCIe, которая имеет 4 разъема USB «Standard A», обычно представляет для системного программного обеспечения один 4-портовый EHCI и два 2-портовых контроллера OHCI. Когда высокоскоростное USB-устройство подключено к любому из 4 разъемов, управление устройством осуществляется через один из 4 портов корневого концентратора контроллера EHCI. Если низкоскоростное или полноскоростное USB-устройство подключено к разъемам 1 или 2, оно будет направлено на порты корневого концентратора одного из контроллеров OHCI для управления, а низкоскоростные и полноскоростные USB-устройства подключены к разъемам. 3 или 4 будут направлены на порты корневого концентратора другого контроллера OHCI. Зависимость EHCI от отдельных хост-контроллеров для высокоскоростных USB-устройств и группы низкоскоростных и полноскоростных USB-устройств приводит к сложным взаимодействиям и зависимостям между драйверами EHCI и OHCI / UHCI.

Поддержка потоковой передачи

Поддержка Streams была добавлена в спецификацию USB 3.0 SuperSpeed, в первую очередь для обеспечения высокопроизводительных операций хранения через USB. Обычно между оконечной точкой USB и буфером в системной памяти существует соотношение 1: 1, и главный контроллер несет полную ответственность за управление всеми передачами данных. Потоки изменили эту парадигму, предоставив связь 1 ко многим «конечная точка с буфером» и позволив устройству указывать хост-контроллеру, какой буфер перемещать. Передачи данных USB, связанные с конечной точкой USB Stream, планируются xHCI так же, как и любая другая массовая конечная точка, однако буфер данных, связанный с передачей, определяется устройством.

Масштабируемость

Архитектура xHCI была разработана с учетом высокой масштабируемости, способной поддерживать от 1 до 255 USB-устройств и от 1 до 255 портов корневого концентратора. Поскольку каждому USB-устройству разрешено определять до 31 конечной точки, xHCI, поддерживающий 255 устройств, должен поддерживать 7 906 отдельных конечных точек. Классически каждый буфер памяти, связанный с конечной точкой, описывается очередью блоков физической памяти, где очереди требуются указатель заголовка, указатель хвоста, длина и другие регистры для определения своего состояния. Существует много способов определить состояние очереди, однако, если предположить, что для каждой очереди будет 32 байта регистрового пространства, то для поддержки 7 906 очередей потребуется почти 256 КБ. Обычно к системе одновременно подключается лишь небольшое количество USB-устройств, и в среднем USB-устройство поддерживает 3-4 конечных точки, из которых только подмножество конечных точек активны одновременно. XHCI поддерживает состояние очереди в системной памяти как структуры данных контекста конечной точки. Контексты спроектированы таким образом, что они могут кэшироваться с помощью xHCI и «выгружаться» на страницы и выходить в зависимости от активности конечной точки. Таким образом, поставщик может масштабировать свое внутреннее пространство кэша контекста конечной точки xHCI и ресурсы в соответствии с практическими моделями использования, ожидаемыми для их продуктов, а не с архитектурными ограничениями, которые они поддерживают. В идеале пространство внутреннего кэша выбирается таким образом, чтобы при нормальных условиях использования не было подкачки контекста с помощью xHCI. Также активность оконечных устройств USB имеет тенденцию быть нестабильной. То есть в любой момент времени большое количество конечных точек может быть готово к перемещению данных, однако только подмножество активно перемещает данные. Например, конечная точка прерывания IN мыши может не передавать данные в течение нескольких часов, если пользователь находится вне своего рабочего места. Алгоритмы производителя xHCI могут обнаружить это условие и сделать эту конечную точку кандидатом для пейджинга, если другие конечные точки станут заняты.

История

Спецификация Open Host Controller Interface (OHCI) была определена консорциумом компаний (Compaq, Microsoft и National Semiconductor) как открытая спецификация для поддержки устройств USB 1.0. Универсальный интерфейс хост-контроллера (UHCI) относится к спецификации, которую Intel изначально определила как собственный интерфейс для поддержки устройств USB 1.0. Спецификация UHCI в конечном итоге была обнародована, но только после того, как остальная часть отрасли приняла спецификацию OHCI.

Спецификация EHCI была определена Intel для поддержки устройств USB 2.0. Архитектура EHCI была смоделирована по образцу контроллеров UHCI и OHCI, которым требовалось программное обеспечение для построения расписаний транзакций USB в памяти, а также для управления полосой пропускания и распределением адресов. Чтобы избежать избыточных усилий отрасли по определению открытой версии интерфейса хост-контроллера USB 2.0, Intel сделала спецификацию EHCI доступной для отрасли без лицензионных сборов.

История версий

Пререлизы

Спецификация xHCI развивалась до нескольких версий до официального выпуска в 2010 году:

Intel XHCI Mode

материал № 9701

КОММЕНТАРИИ к «Intel XHCI Mode»

ДРУГИЕ МАТЕРИАЛЫ ПО ТЕМЕ

Проявления неисправностей, связанных с данным параметром (0)

IT-WIKI (0)

Параметры BIOS (29)

Описание значений параметров:

Описание значений параметров:

Описание значений параметров:

Параметр включает поддержку ASPM для южного моста материнской платы.

Базовая спецификация PCI Express определяет два уровня ASPM, которые предназначены для обеспечения возможности компенсировать повышенное энергосбережение с быстрым восстановлением до состояния L0.

Описание значений параметров:

— ошибка четности на фазе адреса транзакции,

— ошибка четности на этапе данных транзакции специального цикла,

— серьезные проблемы, кроме четности, обнаруженные устройством PCI,

— критические сбои системы, обнаруженные логикой системной платы

Иными словами, включение данной функции позволяет обнаруживать ошибки, возникающие при передаче данных по шине PCI.

Описание значений параметров:

— Serial Port Settings

— COM Port Settings

— Onboard UART 1/2

— Onboard UART

— Onboard Serial Port

— Change Settings

Описание значений параметров:

— Serial Port

— COM Port

Описание значений параметров:

— Power Up On PCI/PCIE Devices

— Resume by PCIE PME

— PCI Express PME

Описание значений параметров:

PERR# является устойчивым сигналом трех состояний, используемым для сигнализации об обнаружении ошибки четности, связанной с фазой данных. Во время каждой фазы данных транзакции чтения целевой объект передает данные на шину AD. Таким образом, цель состоит в том, чтобы обеспечить правильную четность для инициатора по сигналу PAR, начинающемуся через один такт после подтверждения TRDY# (Target Ready). По завершении каждой фазы данных инициатор обязан зафиксировать содержимое AD (31: 0] и C/BE # [3: 0] и рассчитать ожидаемый паритет в течение тактового цикла, сразу после завершения фазы данных. Затем инициатор фиксирует бит четности, предоставленный целью, из сигнала PAR на следующем переднем фронте тактовых импульсов и сравнивает вычисленную и фактическую четность. Если происходит несовпадение, инициатор затем устанавливает PERR# в течение следующих тактовых импульсов (если это можно сделать с помощью единицы в бите ответа об ошибке четности в его регистре команд.) Утверждение PERR # откладывает завершение каждой фазы данных на два тактовых цикла PCI.

Иными словами, включение данной функции позволяет обнаруживать ошибки, возникающие при передаче данных по шине PCI.

Описание значений параметров:

EHCI по-людски на русском языке

Введение

Всех приветствую. Сегодня хочу поделиться опытом и всё-таки по-моему внятно объяснить про такой, на первый взгляд, простой стандарт для USB 2.0 хост-контроллера.

Изначально можно представить себе что USB 2.0 порт — это всего лишь 4 пина, по двум из которых просто передаются данные(Как, к примеру, COM-порт), но самом деле всё не так, и даже совсем наоборот. USB-контроллер в принципе не даёт нам возможности передавать данные как через обычный COM-порт. EHCI — довольно замысловатый стандарт, который позволяет обеспечить надежную и быструю передачу данных от софта до самого девайса, и в обратную сторону.

Возможно, вам пригодиться эта статья, если, к примеру, вы не имеете достаточных навыков написания драйверов и чтение документации к хардвейру. Простой пример: хотите написать свою ОС для мини-ПК, дабы какая-нибудь винда или очередной дистрибутив линукса не загружали железо, и вы использовали всю его мощь исключительно в своих целях.

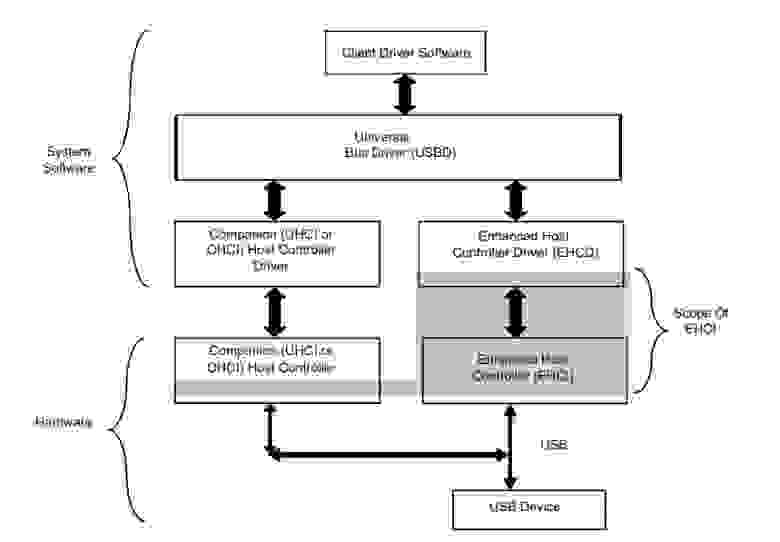

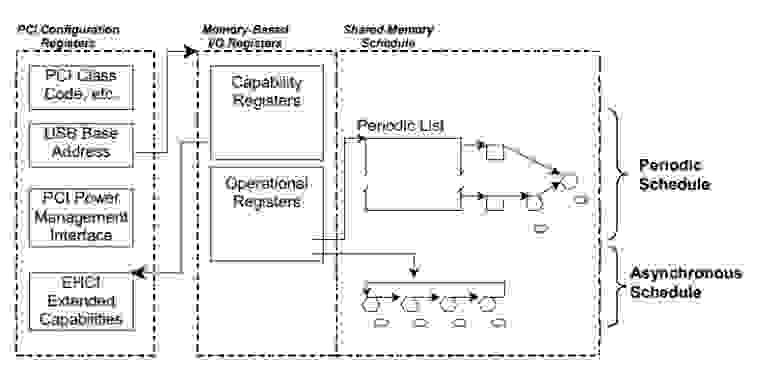

Что такое EHCI

Что же, давайте начнем. EHCI — Enhanced Host Controller Interface, предназначен для передачи данных и управляющих запросов USB-устройствам, и в другую сторону, а в 99% случаев — является связующим звеном, между каким-либо софтом и физическим устройством. EHCI работает как PCI-устройство, а соответственно использует MMIO(Memory-Mapped-IO) для управления контроллером(да-да, я знаю, что некоторые PCI-девайсы используют порты, но тут я всё обобщил). В документации от Intel описан лишь принцип работы, и никаких намеков на алгоритмы, написанные хотя бы на псевдокоде, нет вовсе. EHCI имеет 2 типа MMIO-регистров: Capability и Operational. Первые служат для получения характеристик контроллера, вторые же — для его управления. Собственно, прикреплю саму суть связи софта и EHCI контроллера:

Каждый EHCI контроллер имеет несколько портов, каждому из которых могут быть подключены какие-либо USB-устройства. Так же, прошу заметить, что EHCI является улучшенной версией UHCI, который так же был разработан Intel на несколько годов раньше. Для обратной совместимости любой UHCI/OHCI контроллер, который имеет версию ниже, чем EHCI, будет компаньоном к EHCI. К примеру, у вас есть USB-клавиатура(А большинство клавиатур года так до сих пор были именно такими), которая работает на USB 1.1(заметим, что максимальная скорость работы USB 1.1 — 12 мегабит в секунду, а FullSpeed USB 2.0 имеет пропускную способность аж в 480 мбит/сек), а у Вас имеется компьютер с USB 2.0 портом, при подключении клавиатуры к компьютеру хост-контроллер EHCI как ни как будет работать с USB 1.1. Данная модель показана на следующей схеме:

Так же на будущее хочу сразу предупредить, что Ваш драйвер может работать не правильно из-за такой вот нелепой ситуации: вы инициализировали UHCI, а после чего EHCI, при этом добавили два одинаковых устройства, поставили в регистр порта бит Port Owner Control, после чего UHCI перестал работать, из-за того, что EHCI автоматически перетягивает порт на себя, а порт на UHCI перестаёт откликаться, эту ситуацию надо отслеживать.

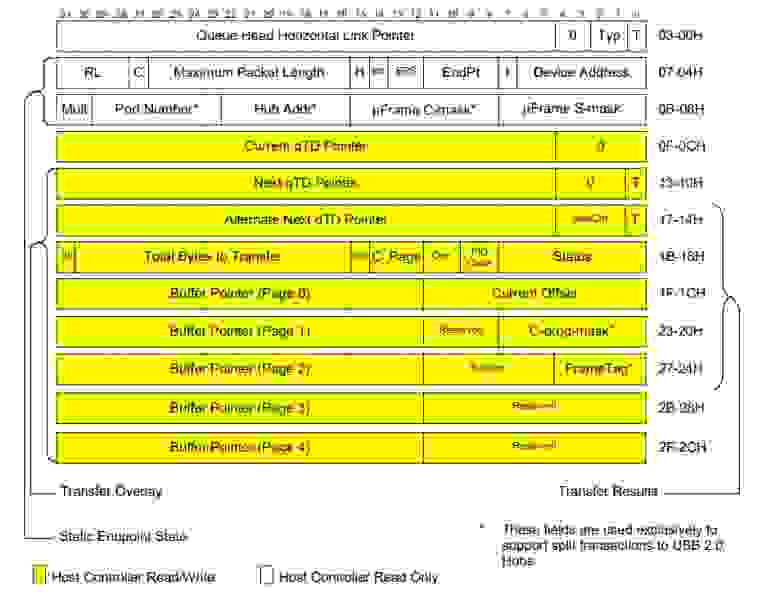

Так же, давайте рассмотрим схему, показывающую саму архитектуру EHCI:

Справа написано про очереди — о них чуть позже.

Регистры EHCI контроллера

Для начала хочется еще раз уточнить, что через данные регистры вы будете управлять вашим устройством, поэтому они очень важны — да и без них программирование EHCI невозможно.

Для начала вам надо получить адрес MMIO, который выдан данному контроллеру, по смещению +0x10 будет лежать адрес наших долгожданных регистров. Есть одно но: сначала идут Capability регистры, а только после них — Operational, поэтому по смещению 0(от предыдущего адреса, который мы получили по смещению 0x10 относительно начала MMIO нашего EHCI) лежит один байт — длина Capability-регистров.

Capability регистры

По смещению 2 лежит регистр HCIVERSION — номер ревизии данного HC, который занимает 2 байта и содержит BCD версию ревизии (что такое BCD можно узнать из википедии).

По смещению +4 лежит регистр HCSPARAMS, его размер — 2 слова, он содержит структурные параметры устройства и его биты показывают следующее:

Operation регистры

По смещению 0 лежит регистр USBCMD — командный регистр контроллера, его биты означают следующее:

По смещению +8 лежит регистр USBINTR — регистр включения прерываний

Чтобы долго не писать, и тем более, Вам долго не читать, значения битов данного регистра можно посмотреть в спецификации, ссылка на неё будет оставлена внизу. Сюда я просто записываю 0, т.к. абсолютно не имею желания писать обработчики, мапить прерывания и т.п., так что это я считаю почти что абсолютно бессмысленным.

По смещению +12(0x0C) лежит регистр FRINDEX, в котором просто лежит текущий номер фрейма, при чем, хочу заметить, что последние 4 бита показывают номер микро-фрейма, в старшие 28 — номер фрейма (так же значение не обязательно меньше размера frameList’а, если вам нужен индекс — лучше брать его с маской 0x3FF(или же 0x1FF, и т.п.).

Регистр CTRLDSSEGMENT лежит по смещению +0x10, он показывает хост-контроллеру старшие 32 бита адреса листа фреймов.

Регистр PERIODICLISTBASE имеет смещение +0x14, в него вы можете положить младшие 32 бита листа фреймов, заметим, что адрес должен быть выравнен по размеру страницы памяти (4096).

Регистр ASYNCLISTADDR имеет смещение +0x18, в него вы можете положить адрес асинхронной очереди, заметим, что он должен быть выравнен по границе 32 байта, при этом должен находиться в первых четырех гигабайтах физической памяти.

Регистр CONFIGFLAG показывает, настроено ли устройство. Вы должны выставить бит 0 после завершения настройки устройства, он имеет смещение +0x40.

Перейдем к регистрам портов. Каждый порт имеет свой командно-статусный регистр, каждый регистр порта располагается со смещением +0x44 + (PortNumber — 1)*4, его биты значат следующее:

Структуры передачи данных и запросов

Организация структуры для обработки запросов включает в себя очередь и трансфер дескрипторы(TDs).

На данный момент мы рассмотрим только 3 структуры.

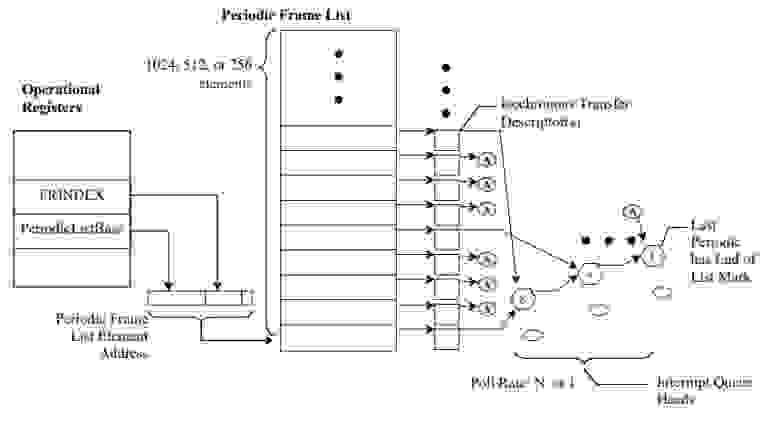

Последовательный список

Последовательный(Периодичный, Pereodic) список устроен следующим образом:

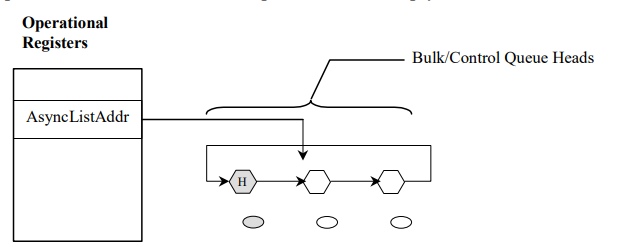

Как видно на схеме, обработка начинается с получения нужного фрейма из фрейм листа, каждый его элемент занимает 4 байта и имеет следующую структуру:

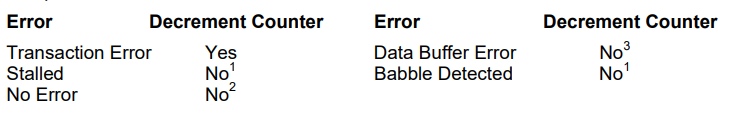

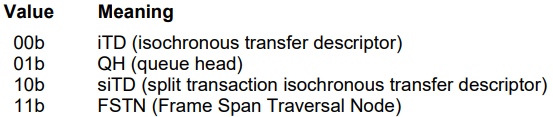

Как видно на картинке, адрес очереди/трансфер дескриптора выровнен по границе 32 байта, бит 0 означает то, что хост-контроллер не будет обрабатывать данный элемент, биты 3:1 показывают тип того, что будет обрабатывать хост-контроллер: 0 — изосинхронный TD(iTD), 1 — очередь, 2 и 3 в данной статье я рассматривать не буду.

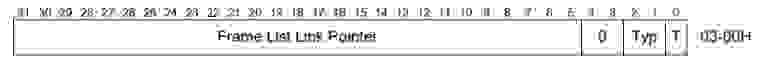

Асинхронная очередь

Хост контроллер обрабатывает данную очередь только тогда, когда фрейм последовательный пустой, либо хост-контроллер обработал весь последовательный список.

Асинхронная очередь представляет собой указатель на очередь, где содержатся другие очереди, которые нуждаются в обработке. Схема:

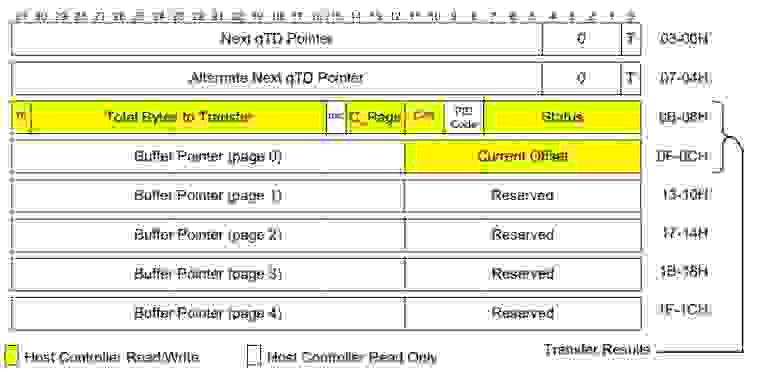

qTD(Queue Element Transfer Descriptor)

Данный TD имеет следующую структуру:

Next qTD Pointer — указатель на продолжение очереди для обработки(для Horizontal Execution), бит 0 Next qTD Pointer’а показывает, то, что дальше нет еще одной очереди.

qTD Token — токен TD, показывает параметры передачи данных:

Голова очереди

Голова очереди(Queue Head) имеет следующую структуру:

Queue Head Horizontal Link Pointer — указатель на следующую очередь, биты 2:1 имеют следующие значения в зависимости от типа очереди:

Endpoint Capabilities/Characteristics — характеристики очереди:

Переходим к самому интересному.

Драйвер EHCI

Начнем с того, какие запросы может выполнять EHCI. Есть 2 типа запросов: Control — а-ля команд, и Bulk — к конечным точкам, для обмена данными, к примеру, абсолютное большинство флешек(USB MassStorage) использует тип передачи данных Bulk/Bulk/Bulk. Мышь и клавиатура для передачи данных тоже используют Bulk — запросы.

Инициализируем EHCI и настраиваем асинхронную и последовательные очереди:

Собственно, код для сброса порта в изначальное состояние:

Control-запрос к устройству:

Код обработки очереди:

И теперь запрос к конечной точке(Bulk-запрос)

Думаю, что тема достаточно интересная, в интернете на русском документаций, описаний и статей на эту тему почти нет, а если есть — очень размыто. Если интересна тема работы с железом и разработки ОС, то есть много чего рассказать.